Будущее ОП – CXL: основа построения компонуемой дезагрегированной памяти (часть 1)

Введение

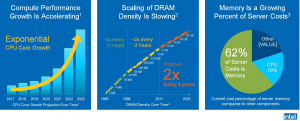

По данным Intel [3] память остается самой дорогостоящей компонентой серверов (рис. 1). На фоне экпоненциального увеличения числа ядер CPU и геометрического роста параметров AI-моделей (которые достигают сотен млрд и более), а также возрастающего спроса на обработку в реальном времени интерес к большему объему ОП будет оставаться еще длительное время.

Рис. 1. Память остается самым дорогостоящей и востребованной компонентой серверов.

После того, как в августе 2022 г. Intel объявила о прекращении производства продуктов на базе технологии Intel® Optane™ встал вопрос о возможных альтернативах их замены. В настоящее время этого можно достичь используя NVDIMM или на базе некоторых технологий SCM типа: MRAM (Samsung), STT-MRAM (Everspin Technologies, https://www.everspin.com/storage-solutions), а также на базе XL-FLASH, созданной на основе технологии 3D флэш-памяти BiCS FLASH™ от KIOXIA (https://europe.kioxia.com/en-europe/business/memory/xlflash.html). Ряд других технологий типа NRAM (Nantero, http://nantero.com/) и др. находятся в стадии разработки.

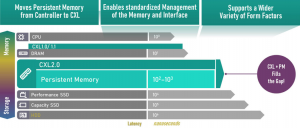

Также следует учитывать, что в настоящее время расширение памяти по DDR-шине (как это было для Intel® Optane™ DC) уходит в прошлое и на смену приходит т.н. Far Near/Memory на базе CXL.

Использование CXL дает возможность дезагрегации серверов и переходу к построению компонуемых инфраструктур, что, в свою очередь, повышает утилизацию ресурсов и снижает стоимость вычислений.

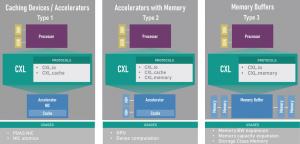

Устройства расширения памяти на базе CXL по классификации консорциума CXL (https://www.computeexpresslink.org/) относятся к устройствам CXL Type 3 (рис. 2). Продукты этого класса дают возможность создать более гибкую и масштабируемую архитектуру памяти, в которой устройства памяти можно добавлять или удалять по мере необходимости без необходимости замены или обновления всей системы. Устройство CXL типа 3 постоянной памяти или вычислительные запоминающие устройства, подключенные к шине CXL, не могут получить доступ к памяти хоста самостоятельно. При этом нужно учитывать, хост тоже должен поддерживать устройства CXL Type 3, что в настоящее время в полной мере обеспечивается только Intel CPU.

Рис. 2. Три типа CXL-устройств (три варианта использования, реализованы в CXL 1.0/1.1), выделяемых консорциумом CXL

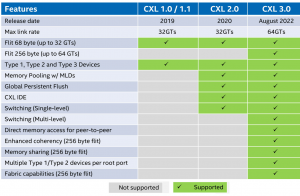

Также следует обращать внимание на поддержку CXL-устройствами типа 3 стандарта CXL 2.0 (в сравнении со стандартом CXL 1.0/1.1), который значительно расширяет возможности CXL 1.1, добавляя CXL Switch, поддержку постоянной памяти и безопасность.

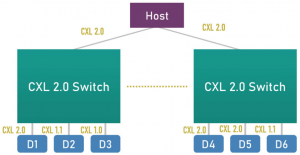

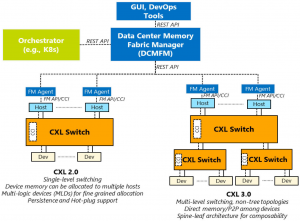

Одной из новых функций CXL 2.0 является поддержка одноуровневого переключения для обеспечения развертывания нескольких устройств (рис. 3). Это позволяет многим устройствам на платформе перейти на CXL, сохраняя при этом обратную совместимость и низкую задержку CXL.

Рис. 3. Коммутатор CXL 2.0 поддерживает разветвление на несколько устройств, сохраняя при этом обратную совместимость.

Одним из важных аспектов набора функций CXL 2.0 является поддержка объединения нескольких логических устройств (MLD, multiple logical devices), а также одного логического устройства с помощью коммутатора CXL, подключенного к нескольким хостам (корневым портам). Эта функция позволяет серверам объединять ресурсы, такие как ускорители и/или память, которые можно назначать различным серверам в зависимости от рабочей нагрузки. Например, если серверу нужны две FPGA и GP-GPU, он может запросить эти ресурсы у менеджера ресурсов в стойке, получить их, если они доступны, и отказаться от них, когда его работа будет выполнена.

Аналогично, память может гибко распределяться и освобождаться между разными серверами (узлами или хостами) в зависимости от необходимости. Это позволяет разработчикам систем не перегружать каждый сервер в стойке, обеспечивая при этом максимальную производительность. CXL 2.0 позволяет создавать пулы (рис. 4) с помощью коммутаторов, подключенных к множественному логическому устройству типа 3 (MLD). Каждый цвет хоста (H) представляет домен или сервер, который определяет иерархию.

Рис. 4. Объединение устройств CXL в пул с коммутатором CXL 2.0 или без него.

Коммутатор CXL 2.0 может обрабатывать несколько доменов (до 16 таких иерархий могут достигать одного MLD). Устройство MLD типа 3 может поддерживать до 16 доменов на каждом из своих портов CXL. Устройство MLD типа 3 также может разделить свои ресурсы CXL и напрямую подключаться к нескольким хостам, каждый из которых имеет выделенный канал CXL (см. рис. 4). Это помогает обеспечить производительность, идентичную прямому соединению, поскольку задержка коммутатора исключено, что важно для доступа к памяти.

Одной из проблем архитектуры межсоединений «загрузка-хранение», такой как CXL, является обеспечение персистентности (запись данных в постоянную память). CXL 2.0 решает эту задачу благодаря архитектуре потока и стандартному интерфейсу управления памятью для программного обеспечения, позволяя перейти от подхода на основе контроллера к прямому управлению памятью (рис. 5).

Рис. 5. CXL 2.0 addresses persistence in Persistent Memory.

Безопасность является краеугольным камнем успеха любой технологии, учитывая широко распространенные атаки на уязвимости. В CXL 2.0 для этого было сделано очень много благодаря совместной работе с другими организациями, занимающимися отраслевыми стандартами, такими как PCI-SIG и DMTF, чтобы обеспечить удобство взаимодействия с пользователем и одновременно предоставить лучшие механизмы безопасности. CXL 2.0 обеспечивает шифрование канала связи, которое безупречно работает с существующими механизмами безопасности, такими как TLB-устройства (рис. 6).

Рис. 6. Улучшения безопасности в CXL 2.0.

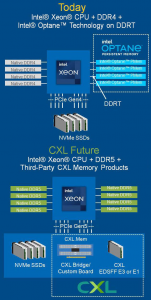

В своих официальных презентационных материалах Intel рассматривает расширение памяти в будущем исключительно на базе CXL с использованием продуктов от третьих фирм (рис. 7,[3]). При этом Intel продолжает работать с экосистемой, чтобы стандарт CXL и модели программирования обеспечивали плавный переход экосистемы от сегодняшнего Intel Optane PMem к завтрашним продуктам памяти, подключаемым к CXL. Аппаратное обеспечение и электрические интерфейсы меняются, но модель программирования многоуровневого хранения памяти остается неизменной [2].

Рис. 7. Расширение памяти в будущем Intel рассматривает исключительно на базе CXL с использованием продуктов от третьих фирм [3].

Среди компаний, продвигающих отдельные направления CXL-решений, можно выделить следующие [3]:

– CXL IP:

- Cadence (https://www.cadence.com);

- FLC Technologies Group (https://flctechgroup.com/);

- Mobiveil (http://mobiveil.com/);

- Rambus (https://www.rambus.com/interface-ip/cxl/cxl2-controller/);

- Synopsys (https://www.synopsys.com/);

- Wolley (http://www.wolleytech.com/, https://www.wolleytech.com/index.php/menu-events-news/news/47-cxl-design);

– CXL Memory Expansion ASIC:

- Astera Labs;

- Intelliprop (https://www.intelliprop.com/products-page);

- Microchip (https://www.microchip.com/en-us/about/news-releases/products/cxl-smart-memory-controllers);

- Montage Technologies (https://www.montage-tech.com/Press_Releases);

- Rambus (https://www.rambus.com/interface-ip/cxl/cxl2-controller/);

- Renesas (https://www.renesas.com/eu/en);

- SK Hynix (https://news.skhynix.com/how-selector-only-memory-emerged-as-the-leading-solution-for-cxl/, https://news.skhynix.com/why-selector-only-memory-is-the-future-for-ultra-fine-processes/, https://news.skhynix.com/sk-hynix-develops-ddr5-dram-cxltm-memory-to-expand-the-cxl-memory-ecosystem/);

- Marvell Technology (https://www.marvell.com/. https://www.marvell.com/search.html?search=cxl);

- Wolley (http://www.wolleytech.com/);

– CXL Memory Module:

- Astera Labs (https://www.asteralabs.com);

- Micron (https://www.micron.com/solutions/server/cxl, https://investors.micron.com/news-releases/news-release-details/micron-launches-memory-expansion-module-portfolio-accelerate-cxl);

- Samsung (samsung.com);

- SK Hynix (https://skhynix.com);

- Smart Modular (https://www.smartm.com/).

CXL – безопасность, доступность данных (CXL IDE, CXL 3.0, GFAM, MAN)

Функции безопасности CXL 2.0 (CXL IDE) [13]

Бурное развитие современных приложений, таких как искусственный интеллект, машинное обучение и глубокое обучение, меняет саму природу вычислений и трансформирует бизнес. Эти приложения открыли компаниям множество способов улучшить процессы развития своего бизнеса, операции, безопасность и качество обслуживания клиентов. Для поддержки этих приложений разрабатываются платформы с использованием SoC, которые могут обрабатывать большие наборы данных в облачных центрах обработки данных, обладают специализированной вычислительной мощностью для обслуживания сценариев использования, создания индивидуальных решений и масштабирования этого рынка. Согласно недавнему отчету Allied Market Research, объем рынка искусственного интеллекта в 2020 году оценивался в $65,48 млрд, а к 2030 году, по прогнозам, достигнет $1 581,70 млрд, при этом среднегодовой темп роста (CAGR) составит 38,0% с 2021 по 2030 год.

С этим экспоненциальным ростом растет обеспокоенность по поводу безопасности на этих платформах, на которых работают критически важные приложения на развивающихся рынках, таких как здравоохранение, автомобилестроение и анализ данных. Безопасность является одним из основных факторов, влияющих на сложность, а также стоимость разработки и обслуживания этих систем. Фактически, согласно отчету IBM Security за 2022 год, средняя глобальная общая стоимость утечки данных увеличилась до $4,35 млн в 2022 году и стала самой высокой в истории. Еще больше беспокоит то, что на выявление нарушения ушло в среднем 207 дней, а на его локализацию — 70 дней.

Помимо стоимости, за последнее десятилетие значительно возросла сложность угроз, которые могут взломать эти платформы злоумышленниками, и ее необходимо решать с помощью конкретных мер безопасности на уровне аппаратного, программного обеспечения и протоколов на платформах SoC.

Угрозы безопасности, преследующие облачно-ориентированные SoC

Задача производителей микросхем заключается не только в разработке высокопроизводительных SoC для облачных приложений, но и в обеспечении функций, которые могут противостоять изощренности векторов угроз для защиты конфиденциальных и конфиденциальных активов на платформах. Большой вопрос, который сейчас задают компании, заключается в том, насколько достаточна безопасность и, даже если устройство изначально будет иметь неповрежденную безопасность, останется ли оно безопасным на протяжении всего своего срока службы.

Это стало очевидным благодаря недавно обнаруженным уязвимостям: Meltdown, Spectre и Foreshadow, основанным на спекулятивном выполнении и предсказании ветвей. Благодаря таким инцидентам было обнаружено, как злоумышленники используют сложные подходы для взлома системы, в которой векторы угроз варьируются от атак вторжения с использованием перехватывающих устройств до атак по побочным каналам, когда информация во время выполнения кода используется для изменения поведения устройства, а также атак, связанных с доступностью. угрозы, включая атаки типа «отказ в обслуживании» (DoS, Denial-of-Service) против систем.

Поскольку эти атаки становятся все более изощренными, стандарты межсоединений следующего поколения, такие как Compute Express Link (CXL), также постоянно адаптируются для защиты от этих угроз, определяя более совершенные протоколы безопасности для обеспечения конфиденциальности, целостности и механизмов шифрования данных (IDE, integrity and data encryption), передаваемых через CXL-связь.

Возможности CXL IDE

Принимая во внимание современные векторы угроз, Консорциум CXL в тесном сотрудничестве с другими организациями, занимающимися отраслевыми стандартами, такими как PCI-SIG и Distributed Management Task Force (DMTF, https://www.dmtf.org/), включил функции целостности и шифрования данных (IDE) в спецификацию CXL 2.0 (рис. 8). Методы IDE обеспечивают сквозную защиту, начиная с самых низких аппаратных уровней системы на кристалле (SoC), и продолжают поддерживать безопасность данных через интерфейс связи и протоколы для всех трех протоколов CXL: CXL.memory, CXL.cache и CXL.io.

Рис. 8. Область применения CXL IDE [13]

Для протоколов CXL.cache и CXL.mem CXL IDE разработана для обеспечения конфиденциальности, целостности и защиты от повторного воспроизведения (replay protection) на уровне FLIT (Flow Control Units, модули управления потоком). FLIT зашифрованы, а целостность защищена с помощью 256-битного криптографического блочного шифра с симметричным ключом AES-GCM (Advanced Encryption Standard, Galois/Counter Mode) и 96-битного кода аутентификации сообщения (MAC, Message Authentication Code), которые предназначены для защиты от атак, перехватывающих пакеты между соединениям “точка-точка” по каналам CXL. Для CXL.io спецификация CXL IDE соответствует PCIe IDE ECN для защиты пакетов уровня транзакций (TLP, Transaction Layer Packets). И PCIe, и CXL поддерживают агрегирование MAC-адресов для оптимизации используемой полосы пропускания.

Кроме того, PCRC пакета добавляется в конец агрегированного открытого текста FLIT, шифруется и включается в вычисление MAC. При реализации на всех устройствах CXL на пути между хостом и конечными точками или между конечными точками, включая промежуточные устройства, такие как коммутаторы, эти меры обеспечивают устойчивость к жестким и мягким сбоям, которые могут быть внесены злоумышленниками с помощью вредоносных методов, таких как побочный канал и шпионские атаки.

В дополнение к этим методам в спецификацию CXL 2.0 были введены два ECN для аутентификации и управления ключами:

– измерение и аутентификация компонентов (CMA, Component Measurement and Authentication) определяет, как протокол безопасности и режим данных (SPDM, Security Protocol and Data Mode) по стандарту DMTF применяются к устройствам/системам CXL;

– обмен объектами данных (DOE, Data Object Exchange) поддерживает транспортировку объектов данных между соединениями CXL.

Эти меры гарантируют, что такие функции, как аутентификация, аттестация, измерение, идентификация и обмен ключами, выполняются в доверенной среде выполнения, образуя доверенную вычислительную базу (TCB, Trusted Computing Base).

Обработка ошибок

CXL IDE предназначена для предотвращения доступа к пользовательским данным, секретам и ключам устройства, когда устройство не проходит проверку целостности. При обнаружении ошибки CXL.cache или CXL.mem IDE ошибка целостности записывается в регистры отчетов об ошибках CXL, весь последующий буферизованный трафик отбрасывается, и устройство уведомляет хост об ошибке, используя методы сигнализации протокола.

Задержки

Хотя безопасность является важным требованием, разработчики систем должны также учитывать потребности в производительности своих систем при включении IDE, что, в зависимости от конкретной выбранной IDE, может привести к дополнительной задержке. Протоколы FLIT с включенной поддержкой IDE поддерживают два отдельных режима работы:

– режим сдерживания (Containment Mode), при котором данные передаются для дальнейшей обработки только после прохождения проверки целостности. Этот режим влияет как на задержку, так и на пропускную способность. Влияние на полосу пропускания связано с тем, что значение целостности отправляется довольно часто;

– Skid Mode, в котором данные передаются для дальнейшей обработки, не дожидаясь получения и проверки значения целостности. Этот режим позволяет менее часто передавать значение целостности. Режим Skid обеспечивает практически нулевую задержку и очень низкую нагрузку на полосу пропускания.

Аппаратная поддержка CXL IDE

В настоящее время опция CXL IDE реализована в составе контроллера Rambus Compute Express Link™ (CXL™) 2.0 (ранее XpressLINK), который использует проверенную архитектуру контроллера PCIe 5.0 для пути CXL.io и добавляет пути CXL.cache и CXL.mem, специфичные для стандарта CXL. Контроллер предоставляет собственный пользовательский интерфейс Tx/Rx для трафика CXL.io, а также интерфейс протокола Intel CXL-cache/mem (CPI) для трафика CXL.mem и CXL.cache. Существует также контроллер CXL 2.0 с версией AXI (ранее XpressLINK-SOC) для реализаций ASIC и FPGA с поддержкой спецификации протокола AMBA AXI для CXL.io и CPI или AXI для CXL.mem и CPI для CXL.cache или спецификация протокола AMBA CXS-B (https://www.rambus.com/interface-ip/cxl/cxl2-controller/).

CXL IDE также реализован в составе IP-ядер Synopsys (https://www.synopsys.com/dw/ipdir.php?ds=security-cxl2-ide).

IP-модуль безопасности целостности и шифрования данных (IDE) Synopsys CXL 2.0 обеспечивает конфиденциальность, целостность и защиту от повторного воспроизведения для FLIT для протоколов CXL.cache и CXL.mem, а также для пакетов уровня транзакций (TLP) в случае CXL.io. Модуль безопасности соответствует спецификации IDE, определенной для CXL 2.0, которая также ссылается на спецификацию PCI Express IDE для протокола CXL.io. Модуль безопасности Synopsys CXL 2.0 IDE легко интегрируется с контроллерами Synopsys CXL для ускорения интеграции SoC.

Модуль безопасности Synopsys CXL 2.0 IDE поддерживает полнодуплексный режим для .cache/.mem/.io и направлений Rx и Tx. Он обеспечивает эффективное шифрование/дешифрование и аутентификацию FLIT и TLP на основе оптимизированных криптографических ядер AES-GCM с малой задержкой, которые специально разработаны для обеспечения оптимального соотношения площади и производительности.

Среди других производителей – AsteraLabs (https://www.asteralabs.com/) с платформой подключения памяти Leo (https://www.asteralabs.com/products/cxl-memory-platform/leo-cxl-memory-connectivity-platform/).

CXL 3.0, GFAM, MAN vs SAN

CXL 3.0, GFAM

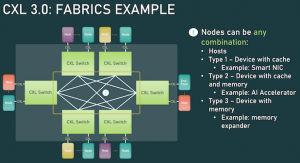

С анонсированием стандарта CXL 3.0 были значительно расширены возможности построения ИТ-инфраструктур на основе CXL, в частности (см. рис. 9) [14]:

– расширены возможности фабрики в части:

- подключаемых к фабрике устстройств и multi-headed устройств;

- улучшения управления фабрикой;

- возможности реализации составной дезагрегированной инфраструктуры;

– улучшены возможности для лучшей масштабируемости и использования ресурсов:

- улучшенное объединение памяти;

- поддержка многоуровневой коммутации;

- новые расширенные возможности когерентности;

- улучшенные возможности ПО;

– удвоение пропускной способности;

– нулевая добавленная задержка по сравнению с CXL 2.0;

– полная обратная совместимость с CXL 2.0, CXL 1.1 и CXL 1.0.

Рис. 9. Функциональность спецификаций CXL 1.0/1.1, CXL 2.0, CXL 3.0.

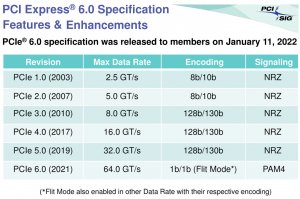

Начиная с физических аспектов CXL, новая версия стандарта CXL 3.0 включает долгожданное обновление для включения PCIe 6.0. Обе предыдущие версии CXL, то есть 1.x и 2.0, были построены на основе PCIe 5.0, поэтому впервые с момента появления CXL в 2019 году его физический уровень был обновлен (рис. 10).

Рис. 10. Ключевые особенности стандарта PCIe 6.0 (https://pcisig.com/pci-express-6.0-specification).

PCIe 6.0 , являющийся крупным обновлением внутренней работы стандарта PCI-Express, еще раз удвоил пропускную способность, доступную по шине, до 64 ГТ/с, что для карты x16 составляет 128 ГБ/с. Это было достигнуто за счет перехода PCIe от использования двоичной (NRZ, non-return-to-zero) сигнализации к четырехуровневой (PAM4, Pulse Amplitude Modulation with Four Levels) сигнализации и включения интерфейса с фиксированными пакетами (FLIT), что позволило удвоить скорость без недостатков работы на еще более высоких частотах. Поскольку CXL, в свою очередь, построен на основе PCIe, это означало, что стандарт необходимо обновить, чтобы учесть эксплуатационные изменения PCIe.

Конечным результатом CXL 3.0 является то, что он унаследовал все улучшения пропускной способности PCIe 6.0, а также все интересные функции, такие как упреждающее исправление ошибок (FEC, Forward Error Correct), что удваивает общую пропускную способность CXL по сравнению с CXL 2.0.

Примечательно, что, по данным Консорциума CXL, им удалось добиться всего этого без увеличения задержки. Это была одна из проблем, с которыми PCI-SIG столкнулась при разработке PCIe 6.0, поскольку необходимое исправление ошибок увеличивало задержку процесса, в результате чего PCI-SIG использовал форму FEC с малой задержкой. Тем не менее, CXL 3.0 делает еще один шаг вперед в попытке уменьшить задержку, в результате чего версия 3.0 имеет ту же задержку, что и CXL 1.x/2.0.

Помимо базового обновления PCIe .60, консорциум CXL также изменил размер FLIT. В то время как CXL 1.x/2.0 использовал относительно небольшой пакет размером 68 байт, CXL 3.0 увеличил его до 256 байт. Гораздо больший размер FLIT является одним из ключевых изменений связи в CXL 3.0, поскольку он дает стандарту гораздо больше битов в заголовке FLIT, которые, в свою очередь, необходимы для реализации сложных топологий и структур, представленных стандартом 3.0. В качестве дополнительной функции CXL 3.0 также предлагает «вариантный» режим FLIT с малой задержкой, который разбивает CRC на 128-байтовые «детализированные передачи суб-FLIT», что предназначено для уменьшения накладных расходов на промежуточное хранение на физическом уровне.

Примечательно, что размер FLIT в 256 байт обеспечивает совместимость CXL 3.0 с PCIe 6.0, который сам использует FLIT в 256 байт. Как и его базовый физический уровень, CXL поддерживает использование большого FLIT не только с новой скоростью передачи данных 64 ГТ/с, но также со скоростями 32, 16 и 8 ГТ/с, что, по сути, позволяет использовать новые функции протокола с более медленными скоростями передачи.

Наконец, CXL 3.0 полностью обратно совместим с более ранними версиями CXL. Таким образом, устройства и хосты могут по мере необходимости переходить на более раннюю версию, чтобы соответствовать остальной части аппаратной цепочки, хотя при этом теряются новые функции и скорости.

CXL 3.0: улучшенная когерентность, совместное использование памяти, многоуровневые топологии и структуры.

Стандарт CXL 3.0 обновил протокол когерентности кэша для устройств с памятью (Type-2 и Type-3). Улучшенная когерентность (Enhanced coherency) позволяет устройствам аннулировать данные, кэшируемые хостом. Это заменяет подход когерентности, основанный на смещении, использовавшийся в более ранних версиях CXL, который поддерживал когерентность не столько за счет совместного управления пространством памяти, сколько за счет того, что хост или устройство отвечали за контроль доступа. Обратная инвалидация (Back invalidation) гораздо ближе к истинному разделяемому/симметричному подходу, позволяющему устройствам CXL информировать хост, когда устройство внесло изменение.

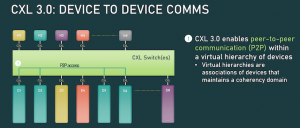

Включение обратной инвалидации также открывает двери для новых одноранговых соединений между устройствами. В CXL 3.0 устройства теперь могут напрямую обращаться к памяти друг друга без необходимости проходить через хост, используя улучшенную семантику согласованности для информирования друг друга о своем состоянии (рис. 11). Пропуск хоста не только быстрее с точки зрения задержки, но и это означает, что устройства не используют драгоценную полосу пропускания между хостом и коммутатором своими запросами.

Рис. 11. CXL 3.0 делает возможной прямую коммуникацию между устройствами.

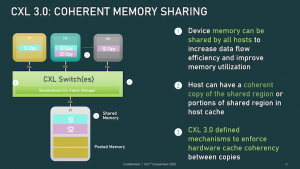

Наряду с настройкой функциональности кэша, CXL 3.0 также представляет некоторые важные обновления для совместного использования памяти между хостами и устройствами. В то время как CXL 2.0 предлагал объединение памяти, при котором несколько хостов могли получить доступ к памяти устройства, но каждому нужно было назначить свой собственный выделенный сегмент памяти, CXL 3.0 обеспечивает истинное совместное использование памяти. Используя новую улучшенную семантику согласованности, несколько хостов могут иметь согласованную копию общего сегмента с обратной инвалидацией, используемой для синхронизации всех хостов, если что-то изменится на уровне устройства (рис. 12).

Рис. 12. Когерентное разделение памяти в CXL 3.0.

Следует отметить, что это не полностью заменяет объединение в пулы. Все еще существуют случаи использования, когда объединение в пулы в стиле CXL 2.0 было бы предпочтительнее (поддержание согласованности требует компромиссов), а CXL 3.0 поддерживает смешивание и сопоставление двух режимов по мере необходимости.

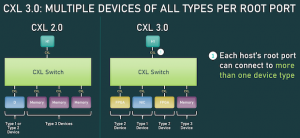

Продолжая расширять эту улучшенную функциональность хост-устройства, CXL 3.0 устраняет предыдущие ограничения на количество устройств типа 1/типа 2, которые могут быть подключены к одному корневому порту CXL. В то время как CXL 2.0 допускал присутствие только одного из этих обрабатывающих устройств после корневого порта, CXL 3.0 полностью снимает эти ограничения. Теперь корневой порт CXL может поддерживать полную комбинированную настройку устройств типа 1/2/3, в зависимости от целей сборщика системы. В частности, это означает возможность подключить несколько ускорителей к одному коммутатору, повысить плотность (больше ускорителей на хост) и сделать новые функции одноранговой передачи гораздо более полезными (рис. 13).

Рис. 13. Поддержка подключения всех типов устройств на корневой порт в CXL 3.0.

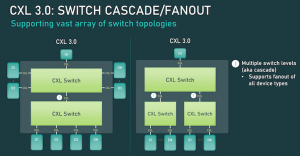

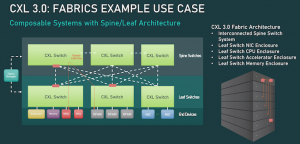

Еще одно важное изменение в CXL 3.0 — поддержка многоуровневого переключения. Это основано на CXL 2.0, в котором введена поддержка коммутаторов протокола CXL, но разрешено размещение только одного коммутатора между хостом и его устройствами. С другой стороны, многоуровневая коммутация позволяет использовать несколько уровней коммутаторов, то есть коммутаторы, подключаемые к другим коммутаторам, что значительно увеличивает виды и сложность поддерживаемых сетевых топологий (рис. 14).

Рис. 14. Поддержка многоуровневого подключения в CXL 3.0.

Даже при наличии всего лишь двух уровней коммутаторов этой гибкости достаточно для реализации топологий, не являющихся древовидными, таких как кольца, сетки и другие конфигурации структуры. А отдельные узлы могут быть хостами или устройствами без каких-либо ограничений по типам (рис. 15).

Рис. 15. Пример недревовидной топологии в CXL 3.0

Между тем, для действительно экзотических конфигураций CXL 3.0 может даже поддерживать архитектуру позвоночника/листа, где трафик маршрутизируется через узлы позвоночника верхнего уровня, единственная задача которых заключается в дальнейшей маршрутизации трафика обратно на узлы нижнего уровня (листья), которые, в свою очередь, содержат реальные хосты/устройства (рис. 16).

Рис. 16. CXL 3.0 может поддерживать архитектуру spine/leaf (корень/лист).

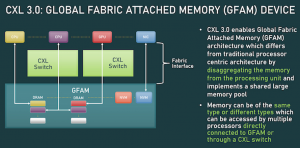

Наконец, все эти новые возможности памяти и топологии/фабрики могут использоваться вместе. Это консорциум CXL называет глобальной памятью, подключенной к фабрике (GFAM, Global Fabric Attached Memory). GFAM выводит идею платы расширения памяти CXL (Type-3) на новый уровень за счет дальнейшего разделения памяти от данного хоста. В этом отношении устройство GFAM функционально представляет собой собственный общий пул памяти, к которому хосты и устройства могут обращаться по мере необходимости. Устройство GFAM может содержать как энергозависимую, так и энергонезависимую память, например, DRAM и флэш-память (рис. 17).

Рис. 17. CXL 3.0: GFAM.

GFAM, в свою очередь, позволит использовать CXL для эффективной поддержки больших многоузловых установок. GFAM позволяет CXL 3.0 обеспечивать необходимую производительность и эффективность для реализации MapReduce в кластере компьютеров, подключенных к CXL. MapReduce, конечно, является очень популярным алгоритмом для использования с ускорителями, поэтому расширение CXL для лучшей обработки рабочей нагрузки, общей для кластерных ускорителей, является очевидным (и, возможно, необходимым) следующим шагом для стандарта. Хотя это немного размывает границы между тем, где заканчивается локальное межсоединение, такое как CXL, и начинается сетевое соединение, такое как InfiniBand.

Самым большим отличием в CXL 3.0 может быть количество поддерживаемых узлов. Механизм адресации CXL, который консорциум называет маршрутизацией на основе портов (PBR, Port Based Routing), поддерживает до 2^ 12 (4096) устройств. Таким образом, установка CXL может масштабироваться только до определенного момента, особенно если ускорители, подключенная память и другие устройства быстро поглощают порты.

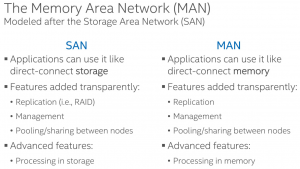

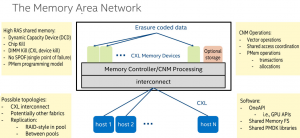

MAN vs SAN

С анонсированием версии CXL 3.0 стало возможным построение компонуемых дезагрегированных инфструктур, и в качестве одного из пулов такой системы может быть память. В этой связи Intel стала продвигать термин Memory Area Network (MAN) по аналогии с SAN (Storage Area Network) (рис. 18).

Рис. 18. Сравнение SAN и MAN [14].

Концепция использование пула/совместного использования памяти CXL включает:

– функции устройства памяти, аналогичные тем, которые SAN сделала для хранения данных: например, прозрачная репликация, более высокий уровень RAS, расширенное управление;

– обеспечение многоуровневого распределения памяти для уменьшения задержки «далекой» (far) памяти CXL (IHV могут предоставлять функции многоуровневого управления для повышения ценности своих продуктов);

– поддержка программируемой модели PMem (реализация может использовать либо энергозависимый, либо энергонезависимый носитель);

– возможность встраивания функции Compute Near Memory (CNM) в объединенную память: возможность совместно использовать логику и память CNM между хостами – никаких «зависших» ресурсов.

Среди основных характеристик RAS разделяемой памяти MAN (рис. 19):

– Dynamic Capacity Device (DCD);

– Chip Kill;

– DIMM Kill (CXL device kill);

– No SPOF (single point of failure);

– PMem programming model.

Рис. 19. Характеристики MAN [14].

Chipkill — это торговая марка IBM , обозначающая технологию расширенной проверки и исправления ошибок (ECC, error checking and correcting) компьютерной памяти, которая защищает системы компьютерной памяти от любого отказа одной микросхемы памяти, а также от многобитовых ошибок в любой части одной микросхемы памяти. Одна простая схема выполнения этой функции распределяет биты Hamming code ECC-слова по нескольким микросхемам памяти, так что отказ любого отдельного чипа памяти затрагивает только один бит ECC на слово. Это позволяет восстановить содержимое памяти, несмотря на полный выход из строя одного чипа. Типичные реализации используют более сложные коды, такие как код BCH (Bose–Chaudhuri–Hocquenghem codes), который может корректировать несколько битов с меньшими издержками (https://en.wikipedia.org/wiki/Chipkill).

Chipkill часто сочетается с динамическим управлением битами (dynamic bit-steering), так что в случае сбоя микросхемы (или превышения порога битовых ошибок) для замены вышедшей из строя микросхемы используется другая, запасная микросхема памяти. Концепция аналогична концепции RAID, которая защищает от сбоя диска, за исключением того, что теперь эта концепция применяется к отдельным микросхемам памяти. Технология была разработана корпорацией IBM в начале и середине 1990-х годов. Технология Chipkill – важная функция RAS, которая в основном используется на твердотельных накопителях , мэйнфреймах и серверах среднего уровня.

Эквивалентная система от HP называетсяAdvanced ECC и Chipspare. Похожая система от Intel, называемая Lockstep Memory , обеспечивает функцию коррекции данных двух устройств (DDDC, double-device data correction). Подобные системы от Micron , называемые избыточным массивом независимых NAND (RAIN), и от SandForce , называемые RAISE level 2 , защищают данные, хранящиеся на твердотельных накопителях, от выхода из строя любого отдельного флэш-чипа NAND.

Модули DIMM с коррекцией ошибок Chipkill показали меньшую долю модулей DIMM, сообщающих о неисправимых ошибках, по сравнению с модулями DIMM с кодами исправления ошибок, которые могут исправлять только однобитовые ошибки.

Репликация в RAID-стиле может быть реализована в пуле или между пулами.

Исследования в области перспективных архитектур RAM

Достаточно интересные публикации представлены на образовательном портале https://www.betriebssysteme.org/. В частности, по ссылке https://www.betriebssysteme.org/?s=.pdf можно найти публикации:

– Onur Mutlu (ETZ Zurich): Memory Centric Computing;

– Tobias Webel (IBM): The Era of Chiplets and its Impact to Future System Designs;

– Daniel Lohmann (Leibniz-University Hannover) and Christian Dietrich (TUHH): OS Challenges for Modern Memory Systems;

– Onur Mutlu (ETZ Zurich): Memory Centric Computing;

– Kai-Uwe Sattler (TU Ilmenau): How to tame the memory zoo in database systems;

– Olaf Spinczyk and Daniel Friesel (University of Osnabruck): System-Level Performance Models for Disruptive Memory Technologies;

– Lukas Wenzel (Hasso-Plattner Institute): Memory Disaggregation with Coherent Interconnect Technologies;

– Norman May (SAP): Why do memory technologies matter to the SAP HANA database?;

– Andy Rudoff (Intel): Emerging Memory Technologies Built On Compute Express Link (CXL);

– Tobias Webel (IBM): The Era of Chiplets and its Impact to Future System Designs;

– Hannes Reinecke (SUSE): High-performance I/O and System Limits;

– Peter Alvaro (UC Santa Cruz): What not where: Sharing in a world of distributed, persistent memory

OCP Composable Memory Systems (CMS)

В октябре 2022 г. OCP объявил о создании подгруппы по системам компонуемой памяти – OCP Composable Memory Systems (CMS, https://www.opencompute.org/blog/ocp-launches-composable-memory-systems-subgroup) в целях разработки архитектуры памяти и контрольных показателей, способствующих инновациям в вычислительной инфраструктуре центров обработки данных следующего поколения. Эта работа началась в феврале 2021 года, когда была запущена Инициатива будущих технологий (Future Technologies Initiative) – программно-определяемая память (SDM, Software Defined Memory; https://www.opencompute.org/wiki/OCP_Future_Technologies_Initiative/Software_Defined_Memory) для изучения вариантов использования, предпочтений в области межсетевого взаимодействия и системных характеристик таких систем памяти.

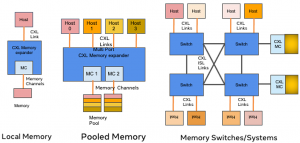

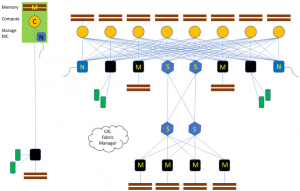

Новые технологии открытых межсоединений (например, CXL) открывают новые возможности подключения памяти (и ввода-вывода, ускорителей) на серверах следующего поколения. Новые межсоединения открывают возможности для новых вычислительных архитектур, особенно для иерархических и многоуровневых архитектур систем памяти, посредством ЦП, буферов памяти CXL, гетерогенных технологий памяти (в рамках единой платформы), а также некоторых будущих потенциальных топологий с переключателями и ускорителями (рис. 20).

Рис. 20. Архитектуры памяти на базе CXL (https://www.opencompute.org/blog/ocp-launches-composable-memory-systems-subgroup).

CXL может обеспечить локальное расширение памяти внутри системы, а также более инновационные решения, позволяющие объединять или совместно использовать память на нескольких хостах.

Проект Composable Memory Systems направлен на реализацию стратегии совместного проектирования аппаратного и программного обеспечения, развитие сообщества для стандартизации и стимулирования внедрения многоуровневых и гибридных технологий и решений памяти, которые могут принести пользу приложениям центров обработки данных в таких отраслях, как AI-ML/HPC, виртуализация серверов и Cache/Databases.

Целью проекта является объединение сообщества операторов центров обработки данных, разработчиков приложений, а также компаний, производящих оборудование и полупроводники, для создания архитектуры и номенклатуры, которые будут опубликованы группой как часть спецификации системы компонуемой памяти. Эта группа также предложит тесты, которые позволят проверить такие системы, обеспечивая общую основу для совместной разработки аппаратного и программного обеспечения для инноваций в аппаратных и программных компонентах. Приложения значительно выиграют от производительности и экономической эффективности, обеспечиваемых стандартизированными решениями CMS.

Инициативу OCP CMS поддержали многие компании, являющиеся действующими членами OCP, в том числе Meta, Microsoft, Intel, Micron, Samsung, AMD, VMware, Uber, ARM, SMART Modular, Cisco и MemVerge.

В октябре 2023 г. OCP CMS представила ряд документов, среди которых (https://www.opencompute.org/wiki/Server/CMS):

– OCP CMS End User Use Cases White Paper [18];

– OCP CMS Workloads and Benchmarks White Paper;

– OCP CMS Logical System Architecture White Paper [17];

– OCP CMS Hotness Tracking Requirements White Paper.

OCP CMS Logical System Architecture [17]

Архитектура логической системы OCP CMS была разработана в диалоге со всем сообществом OCP CMS, и данный документ [17] представляет собой исходную логическую архитектуру. Модели использования CMS только зарождаются, поэтому этот документ со временем будет развиваться в сценариях развертывания для создания компонуемых систем памяти на основе CXL. Архитектура логической системы OCP CMS закладывает основу для разработки физической архитектуры CMS для различных развертываний, уделяя особое внимание совместному проектированию аппаратного и программного обеспечения.

Архитектура логической системы CMS способствует созданию единообразных компонуемых решений, нейтральных к поставщикам, и обеспечивает высокую степень повторного использования с ПО открытой экосистемы, спецификаций аппаратного форм-фактора и передового опыта.

На быстрорастущем корпоративном и гипермасштабном рынке роль памяти становится все более важной. Приложения с интенсивным использованием данных, такие как искусственный интеллект (ИИ), машинное обучение (ML) и базы данных, расширяют границы производительности серверов. Новые технологии памяти, межсоединения и иерархии, которые обещают расширенную пропускную способность памяти, ее емкость, увеличенную пропускную способность, улучшенный обмен данными и большую масштабируемость – все это отвечает требованиям этих приложений с интенсивным использованием данных. Эти аппаратные инновации предназначены для оптимизации производительности и использования ресурсов базовых технологий физической памяти.

Постоянно растущая вычислительная производительность приводит к увеличению спроса на более высокую производительность памяти, в то время как различные категории приложений требуют увеличения емкости памяти для преодоления ограничений платформы. Инженеры-конструкторы активно ищут сбалансированные системные решения, которые используют потенциал новых технологий, продуктов и возможностей программного обеспечения, чтобы позволить этим приложениям максимально эффективно использовать технологии памяти. Ожидается, что появление нового аппаратного обеспечения, программных решений и абстракций памяти откроет новые ценные предложения для сценариев использования памяти, расширяя границы прозрачности расположения, автоматического многоуровневого использования технологий гибридной памяти и реализации объединенных мощностей с унифицированными пространствами имен.

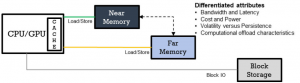

Рис. 21 иллюстрирует взаимодействие программных приложений общего назначения, работающих на CPU или специализированных приложений, таких как искусственный интеллект, работающих на GPU. Понятие «ближайшая память» (“near memory”) относится к памяти, которая находится ближе всего к CPU/GPU, включая такие элементы, как встроенная память с высокой пропускной способностью (HBM, High-Bandwidth Memory) и DRAM хост-системы, подключенные к локальным или удаленным сокетам. И наоборот, «дальняя память» («far memory») находится дальше от CPU/GPU и включает в себя буферы памяти с DRAM, подключенной к Compute Express Link (CXL), памятью класса хранения (SCM), сжатыми страницами памяти в блочных устройствах или объединенной памятью, распределенной по фабрикам CXL. Для оптимизации производительности часто используемые данные обычно хранятся в ближней памяти, а менее часто используемые данные передаются в дальнюю память.

Рис. 21. Иерархия памяти CMS — логическое представление [17].

CMS — это новая парадигма, которая обеспечивает динамическое и унифицированное управление памятью в различных технологиях памяти, межсоединениях и иерархиях. Этот подход удовлетворяет сложные требования к производительности памяти, емкости, задержке, пропускной способности, совместному использованию данных, масштабируемости и безопасности, предъявляемые новыми приложениями, и все это без необходимости перезагрузки сервера. Архитектура логической системы CMS служит жизненно важным ориентиром для проектировщиков систем, операторов центров обработки данных и конечных клиентов при навигации по ландшафту коммерческих внедрений. Первоначальная логическая архитектура CMS в первую очередь ориентирована на приложения общего назначения, работающие на процессорах, и использует межсоединения CXL для реализации вариантов использования пула памяти.

Архитектура логической системы CMS

Логическая архитектура CMS включает абстракции и интерфейсы между различными аппаратными и программными компонентами, необходимыми для реализации компонуемых систем памяти, предназначенных для различных вариантов использования, таких как виртуализация, кэширование/базы данных и AI/ML. Ключевым фактором в архитектуре CMS является Compute Express Link (CXL), открытое и поддерживаемое промышленностью соединение с когерентным кэшем, предназначенное для обеспечения бесперебойной связи между процессорами, ресурсами расширения памяти и ускорителями. CXL предоставляет возможности расширения памяти с использованием семантики загрузки/сохранения памяти, в частности, через протокол cxl.mem, который взаимодействует с хост-системой и базовой операционной системой или средой выполнения гипервизора. Кроме того, CXL.io обеспечивает управление плоскостью управления устройствами и структурой, которую можно использовать для интеграции в оркестровку центра обработки данных для управления парком центров обработки данных.

Логическая архитектура CMS (рис. 22) иллюстрирует пять различных типов компонуемых системных решений, которые используют возможности плоскости данных CXL.mem и абстракции плоскости управления, предоставляемые стандартом CXL. Эти решения включают в себя: 1) прямое подключение; 2) многоголовое соединение; 3) коммутационную структуру; 4) сетевые конфигурации; 5) прямое подключение с использованием транспорта, отличного от физического уровня CXL/PCIe. Каждая из этих конфигураций адаптирует компонуемую систему памяти к конкретным случаям использования и требованиям.

Рис. 22. Архитектура логической системы CMS [17].

Прямое подключение

Это решение представляет собой наиболее простую возможность расширения памяти, при которой устройство CXL напрямую связано с хост-платформой, обслуживая исключительно хост, к которому оно физически подключено. Буферы памяти CXL могут использовать различные технологии памяти, такие как DDR4, DDR5, HBM или SCM. Управление устройством CXL может осуществляться с помощью внутриполосного агента внутри хоста или с помощью внеполосных протоколов с использованием контроллера управления. Выбор предпочтительного метода управления устройствами CXL остается за поставщиками систем. Буфер памяти CXL предоставляет доступ к памяти устройства, управляемого хостом (HDM, host-managed device memory). Прошивка хоста сопоставляет память HDM с согласованным адресным пространством системы, облегчая доступ с хоста с использованием стандартной семантики памяти с обратной записью. Память HDM может быть настроена с помощью встроенного ПО хоста как память специального назначения или как обычная память.

Во время загрузки ядро операционной системы настраивает специальную память CXL HDM как устройство DAX (Direct Access). Утилиты командной строки DAX позволяют увеличивать и уменьшать объем памяти в памяти, управляемой ядром, и из нее после загрузки операционной системы. В любом сценарии обычная память предоставляется как память, управляемая ядром. Области CXL HDM представлены как домены NUMA, занимающие только память. Ожидается, что операционная система или прикладное программное обеспечение будут учитывать атрибуты емкости, пропускной способности и задержки памяти CXL на уровне CXL и реализовывать эффективные алгоритмы многоуровневого распределения для эффективного перемещения данных между хостом и областями памяти CXL.

Прямое подключение с использованием транспорта, отличного от физического уровня CXL/PCIe

Этот вариант использования расширяет ту же логическую архитектурную абстракцию, что и вариант прямого подключения, для транспорта, отличного от физического уровня CXL. Примеры включают UCIe, HBM3, Photonics for Memory Extension (размещение памяти в подходящем физическом месте за счет увеличения расстояния между хостом/ускорителем и памятью), Memory Expansion (расширение памяти; обеспечение большего объема памяти за счет различных типов носителей и использование концепций многоуровневого распределения памяти) и Memory Pooling/Sharing (объединение/совместное использование памяти).

Управление устройством CXL будет осуществляться с помощью тех же внутриполосных или внеполосных методов, которые описаны в других разделах этого документа. В этой модели буфер памяти, отличный от CXL, будет предоставлять доступ к памяти устройства, управляемого хостом (HDM). Прошивка хоста сопоставляет память HDM с согласованным адресным пространством системы, облегчая доступ с хоста с использованием стандартной семантики памяти с обратной записью. Память HDM может быть настроена с помощью встроенного ПО хоста как память специального назначения или как обычная память.

Multi-Headed (многоголовое)

Многоголовый буфер CXL обеспечивает физическую связь с несколькими хостами, тем самым обеспечивая объединение и совместное использование ресурсов памяти между этими хостами. CXL предоставляет логические абстракции для динамического выделения памяти хостам в зависимости от конкретных требований рабочей нагрузки. В тех случаях, когда одна и та же область памяти становится доступной для нескольких хостов, обеспечение согласованности кэша становится обязанностью, разделяемой между хостом, программным обеспечением и/или связанным устройством. Используя ту же логическую абстракцию, этот многоголовый вариант использования также можно расширить до случая «Прямое подключение с использованием другого транспорта» (рис. 23).

Рис. 23. Пример многоголового контроллера памяти в пределах фабрики, подключенной к коммутатору [17].

Фабрика

В отличие от предыдущих подходов к развертыванию, буферы памяти CXL располагаются за коммутатором CXL, который подключается к нескольким хостам и предлагает возможность динамического выделения памяти этим хостам. Память выделяется и предоставляется хостам динамически. Физическое сопоставление и доступ к реальному устройству CXL управляются коммутатором (ами) CXL. Сложность структуры CXL может варьироваться от простого одного коммутатора с возможностью подключения нескольких хостов до сложных иерархических топологий структуры (рис. 24). Эта модель развертывания облегчает объединение и совместное использование, аналогично многоголовому подходу, но с расширенным разветвлением и улучшенным подключением хостов. Менеджер структуры может быть интегрирован в коммутатор, реализован в контроллере управления или в виде программного агента, работающего на любом хосте оркестратора. В конфигурации с несколькими стойками менеджер структуры обеспечивает динамическое выделение памяти в зависимости от требований рабочей нагрузки путем интеграции с агентами менеджера структуры CXL, развернутыми по всему центру обработки данных.

Рис. 24. Примеры моделей развертывания с коммутатором CXL [17].

Сеть

В этой конфигурации развертывания доступ к памяти CXL осуществляется хостом через транспорт памяти по сети. В отличие от предыдущей модели развертывания, прямое подключение к хосту не устанавливается. Хотя эта модель обеспечивает большее разветвление и доступность нескольких стоек, за это приходится платить увеличением задержки. Модели согласованности программного обеспечения могут работать лучше в этой конфигурации с сетевым подключением.

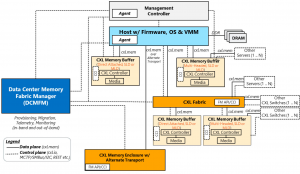

Менеджер фабрики памяти центра обработки данных (DCMFM, Data Center Memory Fabric Manager)

DCMFM служит жизненно важным логическим компонентом для оркестровки памяти. Его основная роль заключается в контроле жизненного цикла ресурсов памяти и оптимизации использования инфраструктуры памяти в центре обработки данных. Этот программный элемент решает различные задачи, включая обнаружение, мониторинг, выделение и отмену выделения ресурсов памяти в среде центра обработки данных. DCMFM действует как плоскость управления, отвечающая за управление критически важными компонентами инфраструктуры памяти, такими как буферы памяти, коммутаторы/фабрики CXL и корпуса памяти (см. рис. 24).

DCMFM контролирует и управляет пропускной способностью и емкостью памяти, а также динамически настраивает конфигурацию структуры памяти в зависимости от требований рабочей нагрузки, определенных оркестратором. Он имеет возможность легко интегрироваться с продвинутыми системами оркестрации, такими как Kubernetes, предлагая администраторам централизованный интерфейс для установки и обеспечения соблюдения политик, распределения ресурсов и управления поведением структуры памяти.

Кроме того, DCMFM выполняет важную функцию по повышению безопасности посредством реализации контроля доступа и мониторинга использования памяти. Он активно способствует повышению комплексной производительности, масштабируемости и адаптируемости центра обработки данных в соответствии с меняющимися требованиями к услугам центра обработки данных.

DCMFM взаимодействует с устройствами физической памяти через агент DCMFM, который может быть программным или встроенным и поддерживает как внутриполосный, так и внеполосный режимы. Взаимодействие с агентом осуществляется через API REST (например, модели DMTF Redfish CXL). Агент использует cxl.io устройства и командный интерфейс компонентов (CCI) для инициирования операций плоскости управления на устройстве CXL. Кроме того, DCMFM реализует меры высокой доступности для устранения любой отдельной точки отказа.

Выделение (обеспечение, provisioning) буфера памяти

В этом разделе описывается одно логическое устройство с прямым подключением к одному хосту (SLD), а также описаны типичные шаги, необходимые для использования буфера памяти CXL операционной системой или приложением. Фактический процесс реализации может варьироваться в зависимости от таких факторов, как тип устройства CXL (буфер памяти, устройство типа 2 или коммутатор), возможности устройства, поддержка протокола CXL и возможности хост-процессора. Буфер памяти CXL должен иметь хотя бы одну память устройства, управляемую хостом (HDM, Host-managed Device Memory), чтобы подключенная к устройству память отображалась в согласованное адресное пространство системы и была доступна с хоста с использованием семантики обратной записи. Буфер памяти CXL может принимать любые поддерживаемые промышленностью форм-факторы модулей памяти и плат расширения памяти.

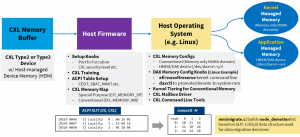

Встроенное (firmware) ПО хоста берет на себя роль настройки различных параметров, таких как разветвление PCIe, чередование и безопасность DFx, связанная с PCIe и CXL (рис. 25). Кроме того, оно инициирует обучение канала и настраивает регистры устройств в соответствии с рекомендациями, указанными в спецификации CXL. После того, как обучение канала успешно завершается, микропрограмма (firmware) хоста приступает к настройке таблиц ACPI, обеспечивая видимость устройств CXL и их конфигураций для операционной системы хоста. В зависимости от конфигурации встроенного ПО хоста карта памяти CXL может быть настроена как память специального назначения (EFI_MEMORY_SP) или обычная (EFI_MEMORY_WB). Операционная система использует эти атрибуты карты памяти для правильной настройки памяти CXL. Обычная память определяется операционной системой как домен NUMA, предназначенный только для памяти, а память специального назначения настраивается как устройство DAX (прямого доступа). Таблица ACPI SLIT предоставляет расстояния NUMA, образуя основу для ядра для повышения и понижения уровня памяти CXL, наряду с другими таблицами ACPI, такими как HMAT.

Рис. 25. Обеспечение буфера памяти CXL (CXL memory buffer provisioning) [17].

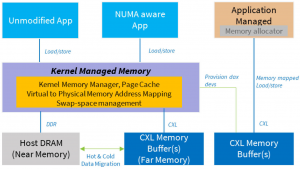

Управление памятью

Ядро несет ответственность за продвижение и понижение уровня данных между уровнями обычной памяти и уровнями CXL, предназначенными только для памяти, на основе политик, настроенных системным администратором (рис. 26). Приложения могут использовать память, управляемую ядром, без каких-либо изменений. Детализированное управление памятью может быть достигнуто с помощью политик numa, поддерживаемых ядром.

Рис. 26. Управление памятью CXL [17].

Память специального назначения настраивается как устройство DAX. Приложения могут отображать память устройства DAX и напрямую использовать память. Cachelib, программное обеспечение с открытым исходным кодом, является примером приложения, которое поддерживает собственное многоуровневое распределение памяти и эффективно управляет памятью CXL. Виртуальные машины — это экземпляры приложений, способные использовать сквозные устройства DAX для использования памяти в гостевой операционной системе. Для выполнения запросов на выделение памяти в регионах памяти DAX приложениям может потребоваться реализовать настраиваемый распределитель памяти. Системные администраторы сохраняют возможность увеличивать и уменьшать объем памяти в памяти, управляемой ядром, и из нее для памяти DAX.

Примеры конкретных развертываний представлены в [18] и [19].

Источники, доп. ресурсы

[1] SDC2022 – Persistent Memories: Without Optane, Where Would We Be? September 12-15, 2022. Presented by Jim Handy, Objective Analysis and Thomas Coughlin, Coughlin Associates – https://www.youtube.com/watch?v=UpgXOhZSgYU; SDC Website: https://storagedeveloper.org/; SNIA Educational Library: https://snia.org/library.

[2] Migration from Direct-Attached Intel® Optane™ Persistent Memory to CXL™ — Attached Memory, Dec. 2022 – https://semiconductor.samsung.com/us/news-events/tech-blog/what-hyperscalers-need-to-know-about-flexible-data-placement-fdp/.

[3] Path to CXL™ ”Maximizing Business Value for Data Centers. January 2023 (Intel-Optane-Usage-Models-CXL-2023.pptx) – https://www.intel.com/content/www/us/en/content-details/757387/path-to-cxl-maximizing-business-value-for-data-centers.html.

[4] Global Non-Volatile Dual In-Line Memory Module (NVDIMM) Market 2023 by Manufacturers, Regions, Type and Application, Forecast to 2029 – https://www.marketresearchreports.com/gir/global-non-volatile-dual-line-memory-module-nvdimm-market-2023-manufacturers-regions-type-and.

[5] GLOBAL DYNAMIC RANDOM ACCESS MEMORY (DRAM) MARKET SIZE & SHARE ANALYSIS — GROWTH TRENDS & FORECASTS (2023 — 2028) – https://www.mordorintelligence.com/industry-reports/dynamic-random-access-memory-market.

[6] Persistent Memory in New Forms and Architectures With CXL. Presented by: Pekon Gupta, SMART Modular Technologies. September 12-15, 2022. SDC2022 – https://www.snia.org/sites/default/files/SDC/2022/SNIA-SDC22-Gupta-Persistent-Memory-New-Forms-and-Architecture-With-CXL.pdf.

[7] SMART Modular Technologies Launches its First Compute Express Link™ Memory Module. Avg. 02 2022 – https://www.smartm.com/media/press-releases/SMART_Modular_Technologies_Launches_its_First_Compute_Express_Link_Memory_Module.

[8] Scaling NVDIMM-N Architecture for System Acceleration in DDR5 and CXL™ — Enabled Systems. Presented by; Arthur Sainio and Pekon Gupta. Persistent Memory + Computational Summit 2022, May 24-25, 2022 – https://www.snia.org/sites/default/files/PM-Summit/2022/PMCS22-Sainio-Gupta-Scaling-NVDIMM-N-Architecture.pdf.

[9] Compute Express Link™ 2.0 White Paper. Nov. 2020 – https://b373eaf2-67af-4a29-b28c-3aae9e644f30.filesusr.com/ugd/0c1418_14c5283e7f3e40f9b2955c7d0f60bebe.pdf.

[10] Micron’s Perspective on Impact of CXL on DRAM Bit Growth Rate. 20.03.2023.

[11] Memory Class Storage is Permanently Changing Server Architectures. 30 sept. 2022 – https://www.nantero.com/wp-content/uploads/NRAM-White-Paper-4-1.pdf.

[12] Persistent Memory for Artificial Intelligence. Bill Gervasi, Principal Systems Architect, 2018 – https://www.nantero.com/wp-content/Documents/20180803_nantero_ai_persistent_memory.pdf.

[13] Insight into CXL 2.0 Security Features and Benefits. Updated: Nov 10, 2022. By Sandeep Dattaprasad, Astera Labs.

[14] Emerging Memory Technology on CXL™. WSOS 2023, Andy Rudoff, Intel Labs – https://www.betriebssysteme.org/wp-content/uploads/2023/05/WSOS_2023_Rudoff.pdf.

[15] Compute Express Link (CXL) 3.0 Announced: Doubled Speeds and Flexible Fabrics, by Ryan Smith on August 2, 2022 – https://www.anandtech.com/show/17520/compute-express-link-cxl-30-announced-doubled-speeds-and-flexible-fabrics.

[16] An Introduction to the Compute Express LinkTM (CXLTM) Interconnect. Debendra Das Sharma Intel, Robert Blankenship Intel, Daniel S. Berger Microsoft Azure – https://arxiv.org/ftp/arxiv/papers/2306/2306.11227.pdf.

[17] CMS: LOGICAL SYSTEM ARCHITECTURE. Version 1.0. Date: Oct 17, 2023. Author (s): Anjaneya Reddy Chagam, Intel Corporation. Reviewers (s): Manoj Wadekar, Meta; Vikrant Soman, Uber; Siamak Tavallaei, Independent – https://docs.google.com/document/d/18kiTJEEGfFr3vAGa5xJuja9_HKfrxg6iXL5F2G8Ug90/edit.

[18] CMS: End User Use Cases. Version 1.0. Date: Oct 17, 2023. Author (s): Manoj Wadekar, Meta; Samir Rajadnya, Microsoft; Vikrant Soman, Uber. Reviewer (s): Anjaneya Reddy Chagam, Intel Corporation; Durgesh Shrivastava, Nvidia; Aran Ziv, Sunrise Corporation. – https://docs.google.com/document/d/1ETqq5IhZC4mmd03CyGPu9k1icnzrKhdir2Ibg9o-b1c/edit.

[19] SDC2022 – Software Defined Memory with CXL and Tiered Memory to Enable Hyperscale Use Cases – https://www.youtube.com/watch?v=OYROR5w7T7U.

Авторы: Гантимуров А.П., Калашник А.Г.

Добавить комментарий

Комментариев пока нет