В конце сентября 2021 г. состоялась ежегодная конференция Storage Developer Conference SNIA (SDC 2021, [1]), на которой были представлены ряд выступлений, посвященных развитию инфраструктуры хранения с использованием протокола CXL 2.0 (Compute Express Link, https://www.computeexpresslink.org).

Введение

Новые и существующие приложения с облачными вычислениями, 5G, IoT, автомобилестроением и высокопроизводительными вычислениями вызывают взрывной рост данных. Эти данные необходимо обрабатывать, перемещать и хранить безопасным, надежным, доступным, экономичным и энергоэффективным способом. Гетерогенная обработка, многоуровневая память и архитектура хранения, ускорители и блоки обработки инфраструктуры необходимы для удовлетворения требований этого развивающегося ландшафта вычислений, памяти и хранения. Эти требования приводят к значительным инновациям в технологиях вычислений, памяти, хранения и межсоединений. Compute Express Link (CXL) с его семантикой памяти и когерентности поверх PCI Express (PCIe) прокладывает путь для конвергенции памяти и хранилища с возможностью вычислений, близких к памяти. Объединение ресурсов с помощью CXL приведет к эффективности масштабирования стойки за счет эффективных механизмов доступа с малой задержкой между несколькими узлами в стойке с расширенной атомарной системой, ускорением, интеллектуальными сетевыми адаптерами и поддержкой постоянной памяти. В этом выступлении мы рассмотрим, как эволюция межсоединений «загрузка-хранилище» существенно изменит ландшафт памяти, хранилища и вычислений в будущем [2].

Тенденции рынка/проблемы эволюции

Тренды в интерконнекте для памяти и СХД

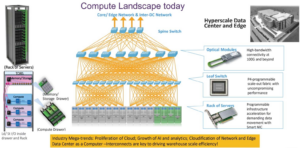

Среди ключевых отраслевые мегатенденций, которые стимулируют развитие новых технологий для интерконнекта ЦОД можно выделить следующие (рис. 1):

- распространение сервис-ориентированных приложений (on-prem/публичные/гибридные облака);

- рост AI/ML/DL-аналитики и аналитики и аналитики больших данных;

- сервисориентированность сети и миграция обработки данных на периферию (edge) являются стимулом развития интерконнекта для поддержания масштабируемости хранилищ данных.

Помимо этого, на развитие интерконнекта влияют такие факторы как:

- использование оптических трансиверов (в том числе со встроенными чипами) с высокой пропускной способностью на уровне 100G, 400G и выше (1600G);

- появление программируемых (на P4) фабрик с горизонтальной масштабируемостью и повышенной производительностью;

- расширение рынка программируемых SmartNIC для создания интеллектуальных фабрик и поддержки обмена данными между компонентами ЦОД без использования CPU.

Рис. 1. Тренды, стимулирующие развитие интерконнекта нового поколения.

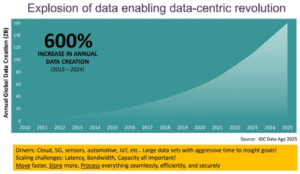

По оценкам IDC, ежегодное увеличение объема данных составляет порядка 600% (рис. 2). Драйверами роста данных являются: облачные сервисы, технология 5G, сенсоры, автономные автомобили, интернет вещей (IoT) и т.д. При этом большие наборы данных требуется обрабатывать за очень малое время (часто в реальном времени) для принятия правильного решения и понимания целей, а масштабирование, время задержки, пропускная способность, емкость – все это становится важным.

Рис. 2. По оценке IDC, ежегодный прирост данных составляет порядка 600%.

Эволюция PCI-Express

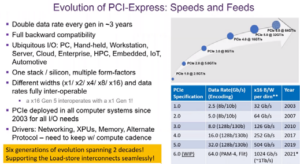

С момента выхода на рынок в 2003 г. эволюция интерфейса PCIe отличалась следующими особенностями (рис. 3):

- удвоение скорости передачи данных для каждого поколения за 3 года;

- поддержка полной обратной совместимости;

- использование PCIe во всех типах компьютерных систем: ПК, портативный компьютер, рабочая станция, сервер, облако, корпоративный ЦОД, высокопроизводительные вычисления, встроенное ПО, интернет вещей, автономные автомобили. PCIe развернут во всех компьютерных системах с 2003 года для всех потребностей ввода/вывода;

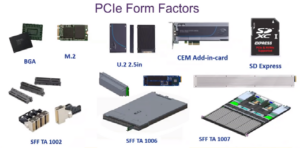

- использование одного стека/чипа для нескольких форм-факторов (рис. 4);

- полная совместимость при различной ширине форм-фактора (x11 x2 / x4 / x8 / x16) и скорости передачи данных (x16 Gen 5 взаимодействует с x1 Gen 1);

- шесть поколений эволюции на протяжении двух десятилетий;

- поддержка прозрачности Load/Store межкомпонентных соединений.

Рис. 3. Эволюция PCIe.

Рис. 4. Использование одной PCIe-спецификации, одного PCIe-стека, одного чипа для множества форм-факторов и различных применений.

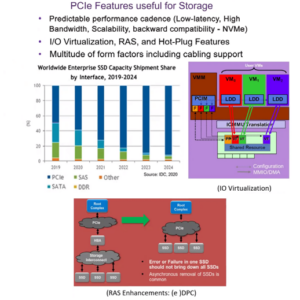

Среди функций PCle полезных для хранения можно отметить следующие (рис. 5):

- предсказуемая производительность и обратная совместимость (NVMe – низкая задержка, высокая пропускная способность, масштабируемость, обратная совместимость);

- виртуализация ввода/вывода, RAS (Reliability, Availability, Serviceability) и функции «горячей» замены;

- множество форм-факторов, включая поддержку кабелей.

При этом, по оценкам IDC, объемы SSD на базе интерфейса к 2024 г. будут подавляющими – более 96% (см. рис. 4).

Рис. 5. Преимущества использования PCIe для SSD.

Технологические аспекты, стимулирующие оптимизацию DRAM

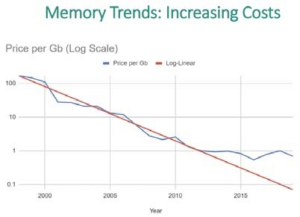

Один из факторов, связанных с эволюцией DRAM – стоимость за гигабит перестала снижаться (рис. 6, [5,6]). Это отчасти связано с возросшим спросом на память на рынке, а отчасти с технологией производства. Это привело:

- к увеличению доли памяти в стоимости системы (неизменная стоимость памяти (стоимость/бит) из-за проблем с масштабированием);

- к увеличению спроса на память из-за увеличения количества ядер CPU, а это, в свою очередь, ведет к:

- увеличению ёмкости памяти;

- увеличению требований к пропускной способности памяти.

Рис. 6. С эволюцией DRAM стоимость за гигабит перестала снижаться.

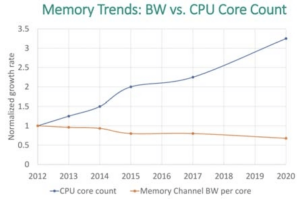

Второй фактор, связанный с эволюцией CPU, это увеличивающийся разрыв между числом ядер CPU и пропускной способностью (Memory Channel bandwidth) памяти на ядро (рис. 7). Он выражается в том, что с эволюцией CPU и ростом производительности его ядер, пропускная способность памяти на ядро снижается [3]. При этом необходимо заметить, что задача увеличения пропускной способности памяти является дорогим удовольствием по следующим причинам:

- добавление каналов в ЦП это:

- большие розетки (увеличение стоимости, снижение надежности);

- увеличение количества слоев печатной платы (дополнительный слой на канал);

- изменение форм-фактор платы (сложность установки при стандартной ширине);

- увеличение скорость передачи данных это:

- усложнение технологии печатных плат (обратное сверление, разъемы SMT, глухие переходные отверстия, более быстрые кросс-сокетные соединения требуют материалов со сверхнизкими потерями – система со сбалансированной полосой пропускания);

- фазовыравнивающая схема / equalization circuits (cложность, добавленная стоимость с обеих сторон);

- 1DPC (проблемы емкости / детализации; экзотические модули DIMM – LR, 3DS).

Чтобы решить эти проблемы с учетом развития новых технологий, был предложен интерфейс CXL, который имеет следующие особенности:

- CXL не зависит от памяти, но имеет согласованный интерфейс;

- CXL позволяет решить проблемы проектирования системы;

- CXL обеспечивает новые архитектуры вычислений и памяти.

Рис. 7. С эволюцией CPU пропускная способность памяти на ядро снижается.

Compute Express Link™ 2.0

В ноябре 2020 г. Консорциум CXL™ выпускает спецификацию Compute Express Link™ 2.0 [4]. CXL 2.0 добавляет новые функции для удовлетворения требований к производительности центров обработки данных следующего поколения, сохраняя при этом обратную совместимость с CXL 1.1 и 1.0.

Основные особенности спецификации CXL 2.0:

- добавлена поддержка переключения для включения разветвления устройств, масштабирования памяти, расширения и миграции ресурсов;

- включена поддержка пула памяти для максимального использования памяти, ограничения или устранения необходимости избыточного выделения памяти, предоставления объема памяти по запросу, поддержка постоянной памяти;

- введена стандартизированная спецификация диспетчера фабрики для инвентаризации и распределения ресурсов, чтобы упростить внедрение и управление коммутаторами и коммутационными решениями на основе CXL;

- обеспечивается стандартизированное управление интерфейсом постоянной памяти и одновременная работа с DDR, освобождая DDR для других целей;

- предоставляется управляемая поддержка горячей замены для перевода устройства CXL в оперативный или автономный режим из системы;

- добавлена целостность и шифрование данных на уровне канала (CXL IDE) для обеспечения конфиденциальности, целостности и защиты от воспроизведения данных, проходящих по каналу CXL;

- включена поддержка широкого спектра отраслевых форм-факторов межсоединений и стандартизированных интерфейсов управления для упрощения внедрения;

- включены спецификации соответствия и функциональной совместимости, а также внутрисистемное тестирование, чтобы создать надежную и функционально совместимую экосистему от различных поставщиков.

«Консорциум CXL с головокружительной скоростью продвигался к выпуску своей спецификации CXL 2.0 второго поколения, даже до того, как продукты, включающие спецификации CXL 1.0 и 1.1 первого поколения, вышли на рынок, – заметил Натан Бруквуд (Nathan Brookwood), научный сотрудник Insight 64. – Новые функции 2.0, включая переключение, объединение памяти и поддержку постоянной памяти, открывают путь для полностью дезагрегированных систем, в которых пулы ускорителей, DRAM и хранилища постоянной памяти могут быть динамически подключены к любому из 16 хост-серверов для удовлетворения требований приложений. Эти функции позволят разработчикам систем изобретать совершенно новые типы систем, о которых архитекторы могли только мечтать всего несколько лет назад».

СXL – это межсоединение открытого отраслевого стандарта, обеспечивающее широкополосную связь с малой задержкой между хост процессором и такими устройствами, как ускорители, буферы памяти и интеллектуальные устройства ввода-вывода. Он предназначен для решения растущих высокопроизводительных вычислительных рабочих нагрузок за счет поддержки гетерогенных систем обработки и памяти с приложениями в области искусственного интеллекта, машинного обучения, аналитики, облачной инфраструктуры, облачности сети и периферии, систем связи и высокопроизводительных вычислений. Это достигается за счет включения семантики когерентности и памяти поверх семантики ввода-вывода на основе PCI Express® (PCIe®) 5.0 для оптимизации производительности в развивающихся моделях использования. Это становится все более важным, поскольку для обработки данных в этих новых приложениях требуется разнообразное сочетание скалярных, векторных, матричных и пространственных архитектур, развернутых в CPU, GPU, FPGA, SmartNIC и других ускорителях [6].

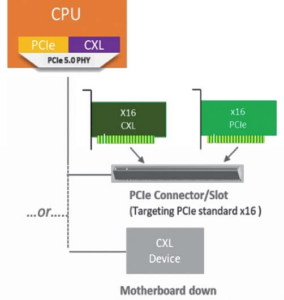

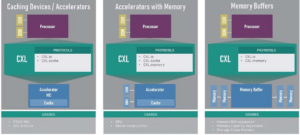

CXL поддерживает как стандартные PCI-eустройства, так и CXL-устройства – все на одной шине (рис. 8).

Рис. 8. CXL поддерживает как PCIe, так и CXL-устройства на одной шине.

CXL 1.0 дебютировал в марте 2019 года, поддерживая динамическое мультиплексирование между богатым набором протоколов, который включает семантику ввода-вывода (CXL.io на основе PCIe), кэширования (CXL.cache) и памяти (CXL.memory). CXL поддерживает единое согласованное пространство памяти между центральным процессором (центральным процессором) и любой памятью подключенного устройства CXL. Это позволяет процессору и устройству совместно использовать ресурсы и работать с одной и той же областью памяти для повышения производительности, уменьшения перемещения данных и уменьшения сложности программного стека, что приводит к трем основным видам использования (рис. 9). Более того, поскольку ЦП в первую очередь является отвечающий за управление согласованностью, он может снизить стоимость и сложность устройства, а также снизить накладные расходы, традиционно связанные с согласованностью каналов ввода-вывода. CXL 1.1, представленный в июле 2019 года, включает детали тестирования на соответствие.

В консорциум CXL входят более 150 компаний членов с активным участием, включая всех CPU и GPU вендоров. CXL 2.0 расширяет возможности CXL 1.1, представляя три основных области: коммутатор CXL, поддержку постоянной памяти и безопасность.

Рис. 9. Типичные случаи использования, разрешенные CXL 1.0 и CXL 1.1.

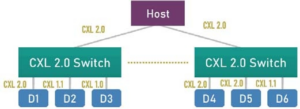

Поддержка обратной совместимости

Одной из новых функций CXL 2.0 является поддержка одноуровневого переключения для включения разветвления на несколько устройств (рис. 10). Это позволит многим устройствам на платформе перейти на CXL, сохраняя при этом обратную совместимость и низкую задержку характеристик CXL.

Рис. 10. Коммутатор CXL 2.0 поддерживает разветвление на несколько устройств при сохранении обратной совместимости.

Поддержка пула нескольких логических устройств

Одним из важных аспектов набора функций CXL 2.0 является поддержка пула нескольких логических устройств (MLD, multiple logical devices), а также одного логического устройства с помощью коммутатора CXL, подключенного к нескольким хостам (корневым портам). Эта функция позволяет серверам объединять ресурсы, такие как ускорители и /или память, которые могут быть назначены разным серверам в зависимости от рабочей нагрузки. Предположим, серверу нужны две FPGA и GPGPU, он может запросить эти ресурсы у диспетчера ресурсов в стойке и получить их, если они доступны, и отказаться от них, когда его работа будет выполнена.

Точно так же память можно гибко распределять и освобождать для разных серверов (то есть узлов или хостов) в зависимости от необходимости. Это позволяет разработчикам системы не перегружать каждый сервер в стойке, обеспечивая при этом наилучшую производительность. CXL 2.0 позволяет объединение в пул с помощью коммутаторов, подключенных к множественному логическому устройству типа 3 (MLD), как показано на рисунке 3. Каждый цвет в узле (H) представляет домен или сервер, который определяет иерархию.

Коммутатор CXL 2.0 может обрабатывать несколько доменов (до 16 таких иерархий могут достигать одного MLD). Устройство MLD типа 3 может поддерживать до 16 доменов на каждом из своих портов CXL. Устройство MLD типа 3 также может разделить свои ресурсы CXL и подключиться напрямую к нескольким хостам, каждый с выделенным каналом CXL, как показано на рисунке 3. Это помогает с производительностью, идентичной прямому подключению, поскольку задержка коммутатора исключено, что важно для доступа к памяти.

CXL 2.0 достигает этих целей, определяя усовершенствования протокола, способные объединяться в пулы, сохраняя при этом качество обслуживания и требования к изоляции надежности для раз личных доменов. Он также определяет управляемые потоки горя чей замены для добавления/удаления ресурсов. Что наиболее важно, CXL 2.0 определяет стандартизованный диспетчер фабрики, чтобы гарантировать, что пользователи будут иметь одинаковый опыт при объединении, независимо от типа устройства, хоста, коммутатора или моделей использования, которые у них есть (рис. 11).

Рис. 11. Объединение устройств CXL в пул с коммутатором CXL 2.0 или без него.

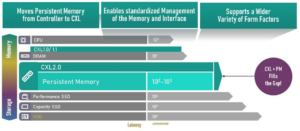

Поддержка энергонезависимой памяти

Одно из важных нововведений в отрасли связано с энергонезависимой памятью, которая приближается к DRAM, например, по характеристикам задержки и пропускной способности, имея преимущество в виде высокой емкости и энергонезависимой памяти. Это позволяет использовать множество высокопроизводительных приложений, в которых весь набор данных может храниться в памяти.

Одной из проблем архитектуры межсоединений «загрузка-хранилище» (load-store), такой как CXL, является обеспечение устойчивости (запись данных в постоянной памяти). CXL 2.0 решает эту задачу за счет продуманного алгоритма и стандартного интерфейса управления памятью для программного обеспечения, что позволяет переместить постоянную память с подхода на основе контроллера к прямому управлению памятью (рис. 12).

Рис. 12. CXL 2.0 решает проблему сохранения данных в постоянной памяти.

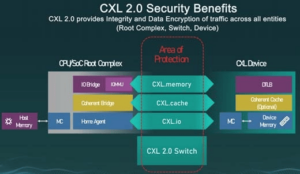

Поддержка безопасности

Безопасность является краеугольным камнем успеха любой технологии, учитывая столь распространенные атаки на уязвимости. CXL делает большие успехи в этом отношении, работая совместно с другими отраслевыми стандартами, такими как PCISIG и DMTF, чтобы обеспечить беспроблемный пользовательский интерфейс, обеспечивая при этом лучшие механизмы безопасности. CXL 2.0 обеспечивает шифрование на канале, которое без проблем работает с существующими механизмами безопасности, такими как TLB устройства (рис. 13). Опубликовав две версии спецификаций за полтора года, Консорциум CXL продвигается вперед за пределы CXL 2.0 и работает над следующей версией CXL 3.0, чтобы охватить более полезные сценарии и обеспечить еще более высокую производительность.

Рис. 13. CXL 2.0 обеспечивает целостность и шифрование данных трафика для всех объектов (Root Complex, Switch, Device).

Расширение функций RAS [5]

Надежность, доступность и удобство обслуживания (RAS, Reliability, Availability, Serviceability) являются важными факторами при проектировании, развертывании и использовании серверов в центрах обработки данных. Экосистема Compute Express Link™ (CXL™) включает в себя множество поставщиков компонентов (SoC, память, хранилище, сеть и т.д.), системных интеграторов и конечных пользователей. CXL позволяет поставщику системы заполнять устройства памяти с разными внутренними архитектурами и мультимедийными технологиями на одной платформе. Можно также использовать разные когерентные ускорители, каждый с потенциально разным типом локальной памяти и от разных поставщиков. Стандарт CXL определяет несколько функций RAS, позволяя всем участникам в этой богатой, разнородной экосистеме вводить новшества в своих областях и при этом взаимодействовать, что в конечном итоге приводит к созданию точек проектирования RAS, отвечающих текущим и возникающим требованиям конечных пользователей.

Конкретные механизмы, используемые для достижения RAS, могут представлять собой смесь инноваций в технологии процессов, архитектуре, встроенном программном обеспечении, системном программном обеспечении, библиотеках и, возможно, прикладном программном обеспечении. Каждый из них может зависеть от поставщика и реализации. Однако проектирование для RAS в рамках поставщика и реализации. Однако проектирование для RAS в рамках обширной экосистемы поставщиков и множества вариантов использования, обеспечиваемых CXL, требует стандартизации некоторых канонических функций RAS, высокой степени видимости ошибок и других событий, связанных с RAS, в наборе компонентов, связанных между собой структурой CXL, а также возможность регистрировать и передавать эти события стандартизированным образом на хост, чтобы разрешить действия RAS на уровне платформы и в рамках операционных потоков на уровне центра обработки данных.

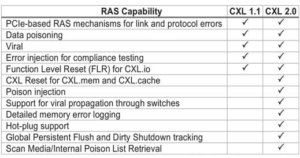

Стандарт CXL 2.0 значительно расширяет функции RAS в сравнении с версией 1.1. Общий список улучшений RAS представлен в табл. 1.

Табл. 1. Сравнение возможностей RAS в CXL 1.1 и в CXL 2.0.

Применения Compute Express Link™ 2.0

Традиционный узел хранения состоит из элементов вычислений, сети и хранения. В этом случае весь узел представляет собой единый домен отказа, и поэтому в хранилище хранятся как данные, так и метаданные. Появление CXL позволяет переосмыслить традиционную архитектуру узлов хранения. В будущем хранилище (за CXL IO) и память метаданных (за памятью CXL) можно будет дезагрегировать локально или по группе узлов хранения, чтобы улучшить доступность данных. Кроме того, постоянство памяти может быть достигнуто на гранулярном уровне с использованием устройств памяти CXL. Будущие расширения CXL с атрибутами, подобными фабрики, могут еще больше расширить возможности репликации данных платформы хранения [8].

Рассмотрим 5 случаев применения CXL.

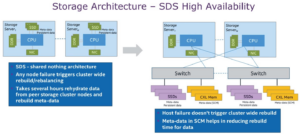

Пример 1. Архитектура хранения – SSD высокой доступности

При подключении SSD в рамках традиционной архитектуры имеются следующие недостатки (рис. 14):

- архитектуру без общего доступа;

- любой сбой узла вызывает перестройку / ребалансировку всего кластера;

- требуется несколько часов для регидратации данных с одноранговых узлов кластера хранения и восстановления метаданных.

Рис. 14. Пример подключение SSD в рамках традиционной архитектуры и через CXL 2.0 с использованием SCM.

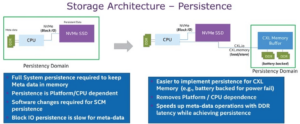

Пример 2. Архитектура хранилища – persistence (постоянство данных)

На рис. 15 представлена традиционная архитектура хранилища и архитектура с использованием CXL для поддержания энергонезависимости данных. В первом случае система имеет следующие особенности:

- полная сохраняемость системы, требует необходимости хранения метаданных в памяти;

- постоянство зависит от платформы / процессора;

- требуются изменения ПО для поддержки SCM;

- поддержка постоянства блочного ввода/вывода медленное для метаданных.

Рис. 15. Пример использования подключения CXL memory buffer с SCM в сравнении с традиционной архитектурой.

При использовании CXL memory buffer получаем следующие пре имущества:

- легче реализовать постоянство для памяти CXL (например, с резервным питанием от батареи на случай сбоя питания);

- устраняется зависимость от платформы/процессора;

- ускоряются операции с метаданными с задержкой DDR, обеспечивая при этом постоянство данных:

- устраняется сложная реализация защиты данных в программном обеспечении (например, журналы транзакций, откаты);

- значительно снижается задержка, требующаяся для интенсивной записи метаданных.

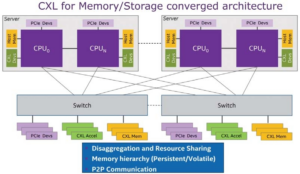

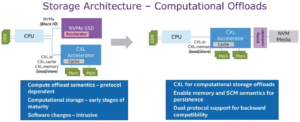

Пример 3. CXL для конвергентной архитектуры памяти/хранилища

С CXL достигаются следующие преимущества (рис. 16):

- дезагрегация и совместное использование ресурсов;

- поддерживается иерархия памяти (постоянная/изменчивая);

- поддерживается P2P-связь (peer-to-peer).

Рис. 16. Пример использования CXL для конвергентной архитектуры памяти/хранилища.

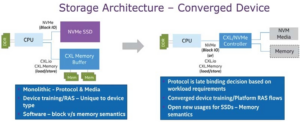

Пример 4. Архитектура хранилища – конвергентное устройство с использованием CXL/NVMe контроллера

На рис. 17 представлена архитектура с и без CXL/NVMe контроллера. В первом случае:

- монолитный протокол и медиа;

- обучение работе с устройством/RAS – уникально для типа устройства;

- ПО – блочная семантика.

Во втором случае:

- протокол, основанный на требованиях рабочей нагрузки;

- поддержка конвергентных устройств / потоков;

- поддержка новых вариантов использования семантики SSD-памяти.

Рис. 17. Пример архитектуры конвергентного устройства с использованием CXL/NVMe контроллера.

Пример 5. Разгрузка CPU – прямое подключение SSD к CXL акселлератору

На рис. 18 представлены преимущества прямого подключения SSD к CXL ускорителю (без использования CPU), в частности:

- устраняется зависимость от протокола;

- реализуется более совершенная архитектура.

Рис. 18. Пример архитектуры с прямым подключением SSD к CXL-ускорителю.

Рис. 18. Пример архитектуры с прямым подключением SSD к CXL-ускорителю.

Заключение:

- CXL открывает возможности для инноваций в архитектуре хранения данных;

- конвергентное устройство хранения/памяти раскрывает потенциал для использования, ориентированного на память;

- ускорители CXL обеспечивают вычислительную архитектуру разгрузки для хранения;

- устройства CXL ускоряют операции с метаданными SDS;

- высокая доступная архитектура для горизонтального масштабирования хранилища с использованием конструкций CXL для сокращения времени перестройки / восстановления в масштабах всего кластера.

Источники, доп. ресурсы

[1] Storage Developer Conference SNIA (SDC 2021), Conference Presentations – https://storagedeveloper.org/events/sdc2021/presentations.

[2] Innovations in Load-Store I/O Causing Profound Changes in Memory, Storage, and Compute Landscape. Dr. Debendra Das Sharma, Intel, SDC 2021 https://www.snia.org/educationalli-brary/innovations-load-store-i-o-causing-profound-changes-memory-storage-and-compute.

[3] Driving Innovations in Compute Platforms with Compute Ex press Link, [CLD006], Intel Innovation 2021; Debendra Das Sharma, Intel Fellow and Director of I/O Technology and Standards, Intel; Chris Petersen, Hardware Systems Technologist, Facebook – https://reg.oneventseries.intel.com/flow/intel/innovation2021/sessioncatalog/page/sessioncatalog/session/1632265372048001bbmB.

[4] CXL™ Consortium Releases Compute Express Link™ 2.0 Specification – https://www.computeexpresslink.org/download-the-specification.

[5] An Overview of Reliability, Availability, and Serviceability (RAS) in Compute Express Link™ 2.0 [February 2021, White paper – https://www.computeexpresslink.org/resource-library.

[6] Compute Express Link™ 2.0 White Paper [November 2020 White paper] – https://www.computeexpresslink.org/resource-library.

[7] Memory Challenges and CXL Solutions [August 2020 – Presentation] – https://www.computeexpresslink.org/resource-library.

[8] SDC2021: Future of Storage Platform Architecture, Mohan Kumar, Intel Fellow, Intel; Anjaneya ‘Reddy’ Chagam, Principal Engineer and Chief SDS Architect, Intel’s Data Center Group / Board Member at SODA Foundation, Intel Corp. – https://www.snia.org/educational-library/future-storage-platform-architecture-2021.

Авторы: Гантимуров А.П., Калашник А.Г.

Отслеживать

Отслеживать